by

Veljko Milutinović

IEEE TCCA Newsletter, September 1996, pp. 1–6.

http://www.computer.org/tab/tcca/tcca.htm

EBI

TYPICAL PROJECT STRUCTURE

Industrial Research:

Phase #1: Survey, and Generation of Embryonic

Ideas

Phase #2: Analytic Analysis and Comparison

Phase #3: Simulation Analysis and Comparison

Phase #4: Implementation Analysis and Comparison

Industrial Design:

fabrication, and post-fabrication testing

Phase #2: Board design, testing, printing, population,

and isolated off-system testing

Phase #3: System software, and in-system board testing

Phase #4: Development of the application software

Skeleton:

1. Introduction

2. Problem Definition

(and About the Importance of the Problem)

3. Existing Solutions

(and Their Critilism from the View-Point

of Interest)

4. Suggested Solution (and its Essence)

5. Conditions and Assumptions

(of the Analysis to Follow)

6. Details of the Compared Solutions (1

+ K)

7. Analytical Analysis (Proofing the Essential

Issues)

8. Simulation Analysis (to Show Performance)

9. Implementational Analysis (to Show Complexity)

10. Conclusion

Important:

1. Skeleton on the Paragraph Level

2. List of References Using the IEEE Standard

3. Object-Oriented Figures with 5-Element

Captions

The Magnificent Seven

Elements of the Set

Operations

Functions

Axioms

Lemmas

Theorem

Corollaries

SOME RECENT PROJECTS

NCR

- Cache coherence maintenance: Hardware approach

- Cache coherence maintenance: Software approach

- Accelerator chip for windowing

- Accelerator board for dbase applications

- Prefetching on the "silence" for disk cacheing

- Accelerator chip for text compression

- Accelerator chip for JPEG/MPEG ENCORE

- Improved RMS for PC, and its prototype

- The RM/MC approach, and its analysis

- Simulation of selected DSM approaches, and their comparison (RMS, KSR, and SCI)

- Search for the optimal RMS inteconnect technology

- TD Technologies i860

- Selected microprocessor models QSI

- An ATM router chip

Legend:

TD—TD Technologies, Inc.

Reference:

[Rose92] Rose, C., Milutinović, V.,

“Personal Communications,”

Internet, Cleveland Heights, Ohio, 1992.

SOME OF THE RECENT REFERENCES

IEEE TUTORIALS:

Tomašević, M., Milutinović., (editors), "Tutorial

on Cache Consistency in Multiprocessor Systems: Hardware Methods,"

IEEE Press, Los Alamitos, California, USA, 1993

(a best seller).

Tartalja, I., Milutinović, V., "Tutorial on Cache

Consistency in Multiprocessor Systems: Software Methods,"

IEEE Press, Los Alamitos, California, USA, 1996.

Protić, J., Tomašević, M., Milutinović, V., "Tutorial

on Distributed Shared Memory: Concepts and Systems,"

IEEE Press, Los Alamitos, California, USA, 1997

(in production).

Ekmečić, I., Tartalja , I., Milutinović, V.,

"Tutorial on Heterogeneous Processing: Concepts and Systems,"

IEEE Press, Los Alamitos, California, USA, 1998

(in preparation).

IEEE JOURNALS:

V. Milutinovic, “Mapping of Neural Networks onto

the Honeycomb Architecture,” Proceedings of the IEEE , Vol. 77, No. 12,

December 1990.

V. Milutinovic, “Tutorial on Microprogramming

and Firmware Engineering,” IEEE Computer Society Press, Los Alamitos, California,

1990.

B. Perunicic, S. Lakhani, V. Milutinovic, “Stochastic

Modeling and Analysis of Propagation Delays in GaAs Adders,”

IEEE Transactions on Computers, Vol. 40, No.

1, January 1991.

V. Milutinovic, D. Fura, W. Helbig, “Pipeline

Design Trade-offs in 32-bit Gallium Arsenide Microprocessor,”

IEEE Transactions on Computers, Vol. 40, No.

11, November 1991.

L. Hoevel, V. Milutinovic, “Terminology Risks

with the RISC Concept in the Risky RISC Arena,”

IEEE Computer, Vol. 25, No. 1, January 1992 (Open

Channel).

M. Tomasevic, V. Milutinovic, “A Survey of

Hardware Solutions for Maintenance of Cache Consistency

in Shared Memory Multiprocessor Systems,” IEEE

MICRO (Part #1), October 1994.

M. Tomasevic, V. Milutinovic, “A Survey of

Hardware Solutions for Maintenance of Cache Consistency

in Shared Memory Multiprocessor Systems,” IEEE

MICRO (Part #2), December 1994.

V. Milutinovic, Z. Petkovic, “Processor Design

Using Silicon Compilation: Ten Lessons Learned from a RISC Design,”

IEEE Computer, Vol. 28, No. 3, March 1995 (Open

Channel).

S. Savic, M. Tomasevic, V. Milutinovic, “Improved

RMS for the PC Environment,”

Microprocessor Systems, Vol. 19, No. 10, September

1995 (A follow up paper will be published in an IEEE journal).

I. Ekmecic, I. Tartalja, V. Milutinovic, “A Taxonomy

of Heterogeneous Computing,” IEEE Computer, Vol. 28, No. 12, December 1995

(Hot Topics).

M. Tomasevic, V. Milutinovic, “The World Invalidate

Protocol,”

Microprocessor Systems, January 1996 (A follow

up paper will be published in an IEEE journal).

A. Grujic, M. Tomasevic, V. Milutinovic, “A Simulation

Study of Hardware DSM Approaches,”

IEEE Parallel and Distributed Technology, Spring

1996.

D. Milutinovic, V. Milutinovic, “Mapping of Interconnection

Networks for Parallel Processing onto the Sea-of-Gates VLSI,”

IEEE Computer, Vol. 29, No. 4, April 1996.

J. Protic, M. Tomasevic, V. Milutinovic, “A Survey

of Distributed Shared Memory: Concepts and Systems,”

IEEE Parallel and Distributed Technology,

Summer 1996.

I. Tartalja, V. Milutinovic, “A Survey of

Software Solutions for Cache Consistency Maintenance in Shared Memory Multiprocessors,”

IEEE Software, January 1997.

V. Milutinovic, “Surviving the Design of a 200MHz

RISC Microprocessor: Lessons Learned,”

IEEE Computer Society Press, Los Alamitos, California,

1996.

I. Ekmecic, I. Tartalja, V. Milutinovic, “A Survey

of Heterogeneous Computing: Concepts and Systems,” Proceedings of the IEEE,

August 1996.

D. Milicev, Z. Petkovic, D. Raskovic, D. Jelic,

D. Jelisavcic, D. Stevanovic, V. Milutinovic, “Modeling of Modern 32-bit

and 64-bit Microprocessors,”

IEEE Transactions on Education, 1997.

V. Milutinovic, “The Best Method for Presentation

of Research Results in Computer Engineering,” IEEE TCCA Newsletter, September

1996.

V. Milutinovic, “Some Solutions for Critical

Problems of Distributed Shared Memory Systems: New Ideas to Analyse,”

IEEE TCCA Newsletter, September 1996.

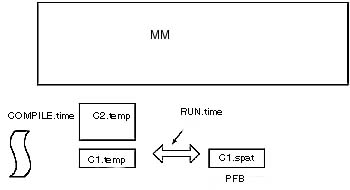

V. Milutinovic, M. Tomasevic, B. Markovic, M.

Tremblay, “The Split Temporal/Spatial Cache Memory for Next Generation

SuperMicroprocessors,”

(To be published). Conference version available

from the Proceedings of the IEEE SCIzzL-5, Santa Clara, California, March

1996.

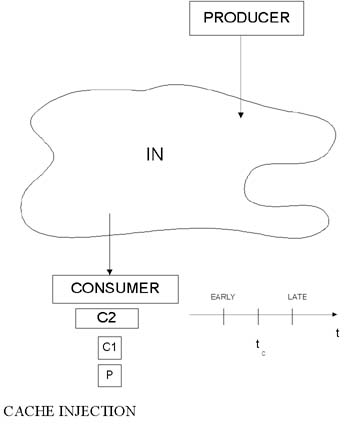

V. Milutinovic, A. Milenkovic, G. Shaeffer, “The

Direct Injection/Replacement Cache Memory for Next Generation SuperMicroprocessors,”

(To be published). Conference version available

from the Proceedings of the IEEE MASCOTS-97, Haifa, Israel, January 1997.

Selected Publications in IEEE Periodicals (only

since 1990)

Note:

Papers from non-IEEE journals have not been listed

here;

listed papers span the areas from advanced processor

design and data communications/networking to cache consistency and distributed

shared memory.

1. V. Milutinovic,

“Mapping of Neural Networks onto the Honeycomb

Architecture,”

Proceedings of the IEEE, December 1989, pp. 1875–1878.

2. D. Gajski, V. Milutinovic, H. J. Siegel, B.

Furht,

“Tutorial on Computer Architecture” (2nd printing),

IEEE Computer Society Press, Los Alamitos, California,

1990 (an IEEE Computer Society best-seller of all times).

3. V. Milutinovic,

“Tutorial on Microprogramming and Firmware Engineering,”

IEEE Computer Society Press, Los Alamitos, California,

1990.

4. B. Perunicic, S. Lakhani, V. Milutinovic,

“Stochastic Modeling and Analysis of Propagation

Delays in GaAs Adders,”

IEEE Transactions on Computers, Vol. 40, No.

1, January 1991, pp. 31-45.

5. V. Milutinovic, D. Fura, W. Helbig,

“Pipeline Design Trade-offs in 32-bit Gallium

Arsenide Microprocessor,”

IEEE Transactions on Computers, Vol. 40, No.

11, November 1991, pp. 1214-1224.

6. V. Milutinovic, L. Hoevel,

“Terminology Risks with the RISC Concept in the

Risky RISC Arena,”

IEEE Computer, Vol. 25, No. 1, January 1992 (Open

Channel), pp. 136–137.

7. M. Tomasevic, V. Milutinovic,

“Tutorial on the Cache Coherency Problem in Shared-Memory

Multiprocessors: Hardware Solutions,”

IEEE Computer Society Press, Los Alamitos, California,

1993.

8. M. Tomasevic, V. Milutinovic,

“A Survey of Hardware Solutions for Maintenance

of Cache Consistency in Shared Memory Multiprocessor Systems,”

IEEE MICRO (Part #1), October 1994, pp. 52–59.

9. M. Tomasevic, V. Milutinovic,

“A Survey of Hardware Solutions for Maintenance

of Cache Consistency in Shared Memory Multiprocessor Systems,”

IEEE MICRO (Part #2), December 1994, pp. 61–66.

10. V. Milutinovic, Z. Petkovic,

“Processor Design Using Silicon Compilation:

Ten Lessons Learned from a RISC Design,”

IEEE Computer, Vol. 28, No. 3, March 1995 (Open

Channel), pp. 120–121.

11. S. Savic, M. Tomasevic, V. Milutinovic,

“RMS for PC,”

Microprocessor Systems, December 1995, pp. 609-619.*

12. I. Ekmecic, I. Tartalja, V. Milutinovic,

“A Taxonomy of Heterogeneous Computing,”

IEEE Computer, Vol. 28, No. 12, December 1995,

pp 68-70.

13. I. Tartalja, V. Milutinovic,

“Tutorial on the Cache Coherency Problem in Shared-Memory

Multiprocessors: Software Solutions,”

IEEE Computer Society Press, Los Alamitos, California,

1996.

14. M. Tomasevic, V. Milutinovic,

“The World Invalidate Protocol,”

Microprocessor Systems, March 1996, pp. 3-16.*

15. A. Grujic, M. Tomasevic, V. Milutinovic,

“A Simulation Study of Hardware DSM Approaches,”

IEEE Parallel and Distributed Technology, Spring

1996, pp. 74–83.

16. D. Milutinovic, V. Milutinovic,

“Mapping of Interconnection Networks for Parallel

Processing onto the Sea-of-Gates VLSI,”

IEEE Computer, Vol. 29, No. 6, June 1996, pp.

112–113.

17. J. Protic, M. Tomasevic, V. Milutinovic,

“A Survey of Distributed Shared Memory: Concepts

and Systems,”

IEEE Parallel and Distributed Technology, Summer

1996, pp. 63–78.

18. I. Ekmecic, I. Tartalja, V. Milutinovic,

“A Survey of Heterogeneous Computing: Concepts

and Systems,”

Proceedings of the IEEE, August 1996, pp. 1124–1144.

19. V. Milutinovic,

“Surviving the Design of a 200MHz RISC Microprocessor:

Lessons Learned,”

IEEE Computer Society Press, Los Alamitos, California,

1996.

20. V. Milutinovic,

“The Best Method for Presentation of Research

Results,”

IEEE TCCS Newsletter, September 1996, pp. 1-6.

21. V. Milutinovic,

“Some Solutions for Critical Problems in the

Theory and Practice of Distributed Shared Memory: New Ideas to Analyze,”

IEEE TCCS Newsletter, September 1996, pp. 7-12.

22. I. Tartalja, V. Milutinovic,

“A Survey of Software Solutions for Cache Consistency

Maintenance in Shared Memory Multiprocessors,”

IEEE Software, January 1997 (accepted).

23. J. Protic, M. Tomasevic, V. Milutinovic,

“Tutorial on DSM: Concepts and Systems,”

IEEE Computer Society Press, Los Alamitos, California,

USA, 1997 (accepted).

24. D. Milicev, Z. Petkovic, D. Raskovic, D.

Jelic, M. Jelisavcic, D. Stevanovic, A. Milenkovic, V. Milutinovic,

“Modeling of Modern 32-bit and 64-bit Microprocessors,”

IEEE Transactions on Education, 1997 (accepted).

25. Milutinovic, V.,

“Surviving the Design of Microprocessor and Multimicroprocessor

Systems: Lessons Learned,”

IEEE Computer Society Press, Los Alamitos, California,

USA, 1997 (accepted).

26. V. Milutinovic, B. Markovic, M. Tomasevic,

M. Tremblay,

“The Split Temporal/Spatial Cache Memory,”

IEEE Transactions on Computers, 1997 (conditionally

accepted).

Conference version available from the Proceedings

of the IEEE MELECON-96, Bari, Italy, May 1996, pp. 1108–1111.

27. Milutinovic, V.,

“A Research Methodology in the Field of Computer

Engineering for VLSI,”

IEEE Transactions on Education, 1997 (conditionally

accepted).

Conference version available from the Proceedings

of the IEEE MIEL-95, Nis, Serbia, Yugoslavia, pp. 811–816.

28. Ekmecic, I., Tartalja, I., Milutinovic, V.,

“Tutorial on Heterogeneous Processing: Concepts

and Systems,”

IEEE Computer Society Press, Los Alamitos, California,

USA, 1997 (conditionally accepted).

General Citations:

SCI—over 50 (excluding self-citations);

BOOKS (including textbooks, monographs, as well

as M.Sc. and Ph.D. theses)—over 100;

INSPEC—over 1000.

Textbook Citations:

Note:

This list includes all textbooks available at

the Stanford University Bookstore and at the Purdue University Bookstore

in Fall 1996

(only the textbooks published on or after 1990),

which include the term Computer Architecture in their title (or subtitles),

and cover the general field of computer architecture.

Legend:

Position X—position of VM in the ranking of referenced

authors (s = shared position);

Y citations—number of VM citations in the textbook

(na = not applicable).

Flynn, M. J., Computer Architecture, Jones and

Bartlett, USA (96)

position 1 (12 citations)

Bartee, T. C., Computer Architecture and Logic

Design, McGraw-Hill, USA (91)

position 1 (2 citations)

Tabak, D., RISC Systems (RISC Processor Architecture),

Wiley, USA (91)

position 1s (6 citations)

Stallings, W., Reduced Instruction Set Computers

(RISC Architecture), IEEE CS Press, Los Alamitos, California, USA (90)

position 1s (3 citations)

Heudin, J. C., Panetto, C., RISC Architectures,

Chapman-Hall, London, England (92)

position 3s (2 citations)

van de Goor, A. J., Computer Architecture and

Design, Addison Wesley, Reading, Massachusetts, USA (2nd printing, 91)

position 4s (3 citations)

Tannenbaum, A., Structured Computer Organization

(Advanced Computer Architecures), Prentice-Hall, USA (90)

position 5s (4 citations)

Feldman, J. M., Retter, C. T., Computer Architecture,

McGraw-Hill, USA (94)

position 7s (2 citations)

Stallings, W., Computer Organization and Architecture,

Prentice-Hall, USA (96)

position 9s (3 citations)

Murray, W., Computer and Digital System Architecture,

Prentice-Hall, USA (90)

position >10s (2 citations)

Wilkinson, B., Computer Architecture, Prentice-Hall,

USA (91)

position >10 (2 citations)

Decegama, A., The Technology of Parallel Processing

(Parallel Processing Architectures), Prentice-Hall, USA (90)

position >10s (2 citations)

Baron, R. J., Higbie, L., Computer Architecture,

Addison-Wesley, USA (92)

position >10s (1 citation)

Tabak, D., Advanced Microprocessors (Microcomputer

Architecture), McGraw-Hill, USA (95)

position >10s (1 citation)

Zargham, M. R., Computer Architecture, Prentice-Hall,

USA (96)

position >10s (1 citation)

Hennessy, J. L., Patterson, D. A., Computer Architecture:

A Quantitative Approach, Morgan-Kaufmann, USA (96)

na (0 citations)

Hwang, K., Advanced Computer Architecture, McGraw-Hill,

USA (93)

na (0 citations)

Kain, K., Computer Architecture, Addison-Wesley,

USA (95)

na (0 citations)

of Research Results

ERRORS

MADE

&

LESSONS

LEARNED

Figure B2: THE most important issue (source: [Rose92]).

Legend: Self-explanatory.

Major IEEE Awards

Fellow of the IEEE

- Eckert-Mauchly: Computer Engineering (Hardware + Architecture)

- Emanuel Piore: Information Sciences (Software + ...)

- Harry Goode: Information Systems (Informatics + ...)

The von Neumann Medal

The Split Temporal/Spatial Cache

Veljko Milutinović, Boris Marković*, Milo Tomašević, Aleksandar Milenković,

and Mark Tremblay**

IFACT

Department of Computer Engineering

School of Electrical Engineering

University of Belgrade

POB 816

11000 Beograde, Serbia, Yugoslavia

* Boris Marković is with the University of Montenegro, Podgorica, Montenegro, Yugoslavia

** Mark Tremblay is with the SUN Microsystems, Palo Alto, California, USA

Veljko Milutinović, Aleksandar Milenković, Davor Magdić, Jasna Ristić-Đurović

and Gad Sheaffer*

IFACT

Department of Computer Engineering

School of Electrical Engineering

University of Belgrade

POB 816

11000 Beograde, Serbia, Yugoslavia

* Gadf Sheaffer if with the Intel Corporation, Beverton, Oregon, USA

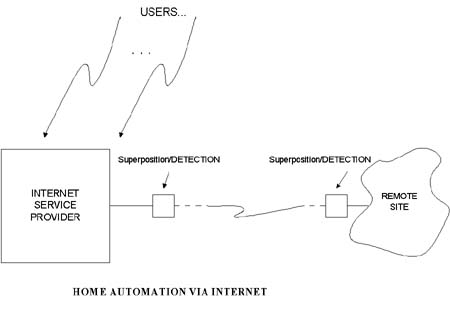

INTERNET/TELEPHONY INTERFACES

Goran Davidović, Veljko Milutinović, Gordana Hadžić, Lazar Radičević,

and Oskar Mencer*

* Stanford University and TELLCO

Reconfigurable FPGA for EBI

Božidar Radunović, Predrag Knežević, Veljko Milutinović,

Steve Casselman and John Schewel*

*MIT and VCC

Intelligent Proxy for EBI

Dejan Petković, Milja Pešić,

and Veljko Milutinović

UCB and Telco

PROXI PREFETCHING/CACHING WITH

SPATIAL/TEMPORAL SELECTION

Genetic Search

with Spatial/Temporal Mutations

Jelena Mirković, Dragana Cvetković,

and Veljko Milutinović

UCLA and Technicom

GENETIC SEARCH WITH SPATIAL/TEMPORAL MUTATION

Drawbacks of INDEX-BASED: Time to index + ranking

Advantages of LINKS-BASED: Mission critical applications + customer

tuned ranking

Well organized markets: Best first

If elements of disorder: G w DB mutations

Disorganized markets: G w S/Tmutations